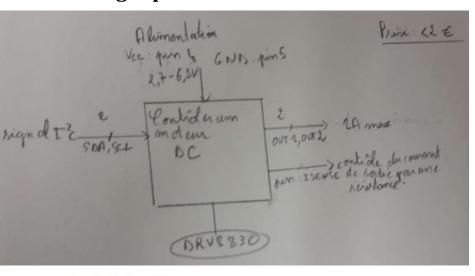

# Circuit intégré pour contrôler moteur courant continu: <u>DRV8830</u>

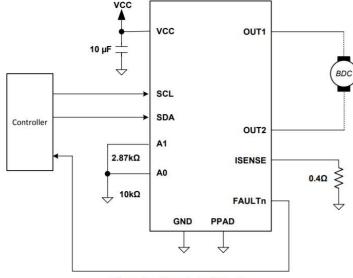

#### 8.2 Typical Application

Figure 11 is a common application of the DRV8830.

Figure 11. Motor Control Circuitry

The HVSSOP package has a PowerPAD.

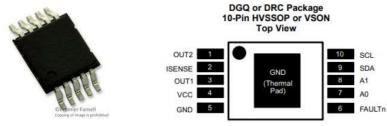

#### Pin Functions

| PIN    |       | TYPE(1) | DESCRIPTION             | EXTERNAL COMPONENTS                                                                |  |

|--------|-------|---------|-------------------------|------------------------------------------------------------------------------------|--|

| NAME   | NO.   | TIPE    | DESCRIPTION             | OR CONNECTIONS                                                                     |  |

| A0     | 7     | i i     | Address set 0           | Connect to GND, VCC, or open to set I <sup>2</sup> C                               |  |

| A1     | 8     | 1       | Address set 1           | base address. See serial interface description.                                    |  |

| FAULTn | 6     | OD      | Fault output            | Open-drain output driven low if fault condition<br>present                         |  |

| GND    | 5     | _       | Device ground           |                                                                                    |  |

| ISENSE | 2     | 10      | Current sense resistor  | Connect current sense resistor to GND.<br>Resistor value sets current limit level. |  |

| OUT1   | JT1 3 |         | Bridge output 1         | Comment to make winding                                                            |  |

| OUT2   | 1     | 0       | Bridge output 2         | Connect to motor winding                                                           |  |

| SCL    | 10    | l l     | Serial clock            | Clock line of I <sup>2</sup> C serial bus                                          |  |

| SDA    | 9     | 10      | Serial data             | Data line of I <sup>2</sup> C serial bus                                           |  |

| vcc    | 4     | -       | Device and motor supply | Bypass to GND with a 0.1-μF (minimum) ceramic capacitor.                           |  |

<sup>(1)</sup> Directions: I = input, O = output, OZ = tri-state output, OD = open-drain output, IO = input/output

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)(2)

|                  |                                                      | MIN               | MAX                | UNIT |

|------------------|------------------------------------------------------|-------------------|--------------------|------|

| vcc              | Power supply voltage                                 | -0.3              | 7                  | V    |

|                  | Input pin voltage                                    | -0.5              | 7                  | V    |

|                  | Peak motor drive output current <sup>(3)</sup>       | Internally limit  | Internally limited |      |

|                  | Continuous motor drive output current <sup>(3)</sup> | -1                | 1                  | Α    |

|                  | Continuous total power dissipation                   | See Thermal Infor | mation             |      |

| TJ               | Operating virtual junction temperature               | -40               | 150                | °C   |

| T <sub>stq</sub> | Storage temperature                                  | -60               | 150                |      |

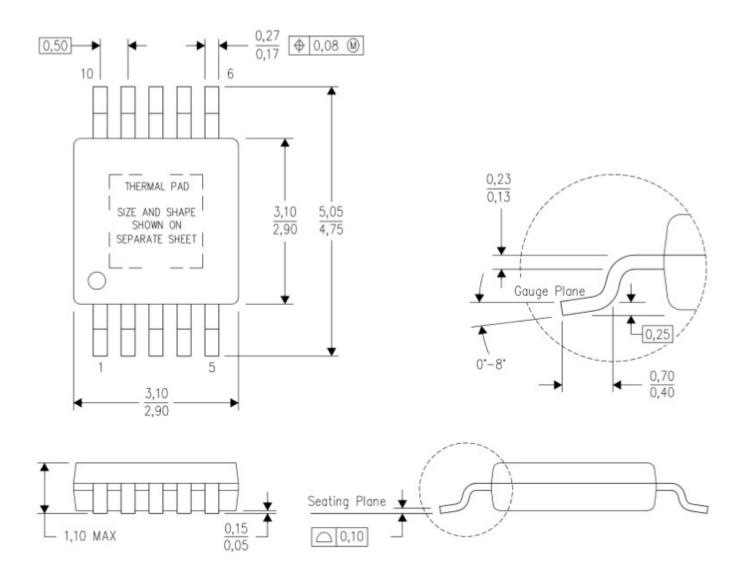

10.2 Layout Example

Figure 18. Layout Recommendation

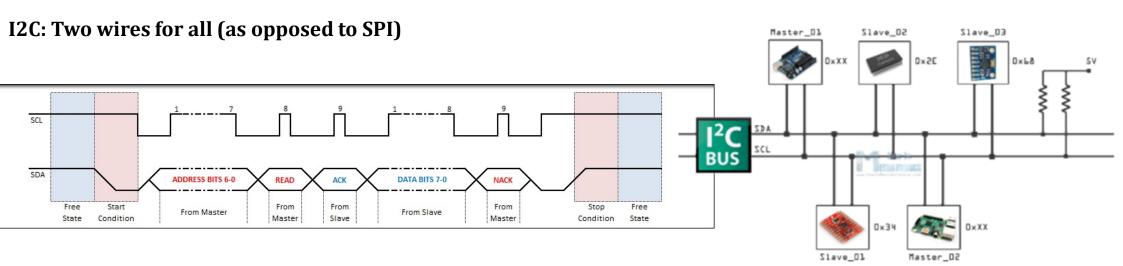

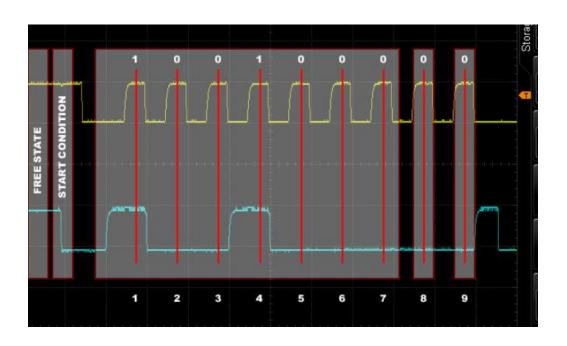

# I2C: Two wires for all (as opposed to SPI)

# Wire Library

# **Functions**

- begin()

- requestFrom()

- beginTransmission()

- endTransmission()

- write()

- available()

- read()

- SetClock()

- onReceive()

- onRequest()

# **DRV8830 I2C**

DRV8830

w.ti.com SLVSAB2G – MAY 2010 – REVISED DECEMBER 2015

The upper address bits of the device address are fixed at 0xC0h, so the device address is as follows:

Table 5. Device Addresses

| A1 PIN | A0 PIN | A3A0 BITS<br>(as below) | ADDRESS (WRITE) | ADDRESS (READ) |

|--------|--------|-------------------------|-----------------|----------------|

| 0      | 0      | 0000                    | 0xC0h           | 0xC1h          |

| 0      | open   | 0001                    | 0xC2h           | 0xC3h          |

| 0      | 1      | 0010                    | 0xC4h           | 0xC5h          |

| open   | 0      | 0011                    | 0xC6h           | 0xC7h          |

| open   | open   | 0100                    | 0xC8h           | 0xC9h          |

| open   | 1      | 0101                    | 0xCAh           | 0xCBh          |

| 1      | 0      | 0110                    | 0xCCh           | 0xCDh          |

| 1      | open   | 0111                    | 0xCEh           | 0xCFh          |

| 1      | 1      | 1000                    | 0xD0h           | 0xD1h          |

The DRV8830 does not respond to the general call address.

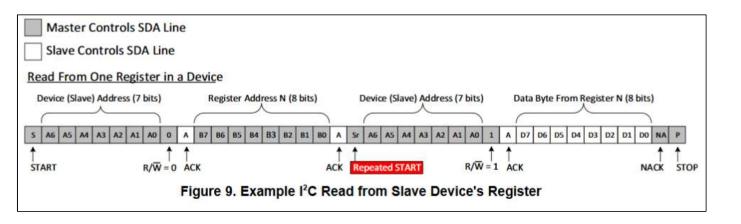

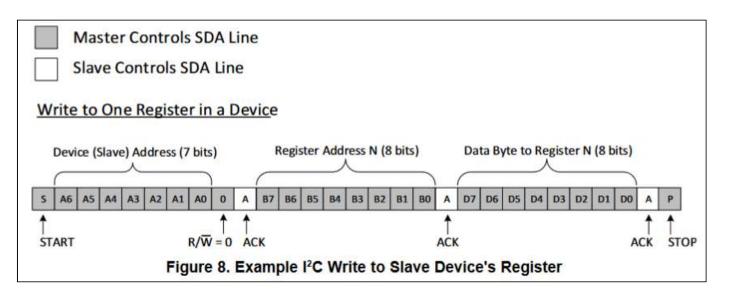

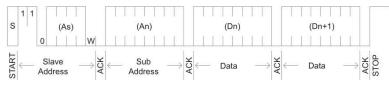

A data byte follows the address acknowledge. If the R/W bit is low, the data is written from the master. If the R/W bit is high, the data from this device are the values read from the register previously selected by a write to the subaddress register. The data byte is followed by an acknowledge sent from this device. Data is output only if

Figure 9. I<sup>2</sup>C Read Mode

Figure 10. I<sup>2</sup>C Write Mode

## 7.6 Register Maps

## 7.6.1 I<sup>2</sup>C Register Map

Table 6. I<sup>2</sup>C Register Map

| REGISTER | SUB ADDRESS (HEX) | REGISTER NAME | DEFAULT VALUE | DESCRIPTION                                     |

|----------|-------------------|---------------|---------------|-------------------------------------------------|

| 0        | 0x00              | CONTROL       | 0x00h         | Sets state of outputs and output voltage        |

| 1        | 0x01              | FAULT         | 0x00h         | Allows reading and clearing of fault conditions |

### 7.6.1.1 REGISTER 0 - CONTROL

The CONTROL register is used to set the state of the outputs as well as the DAC setting for the output voltage. The register is defined as follows:

Table 7. Register 0 - Control

| Table 7. Register 0 - Control |     |     |  |  |  |  |

|-------------------------------|-----|-----|--|--|--|--|

| D7 - D2                       | D1  | D0  |  |  |  |  |

| VSET[50]                      | IN2 | IN1 |  |  |  |  |

Table 4. H-Bridge Logic

OUT2

**FUNCTION**

OUT1

| 0 | 0 | Z | Z | Standby / coast |

|---|---|---|---|-----------------|

| 0 | 1 | L | Н | Reverse         |

| 1 | 0 | Н | L | Forward         |

| 1 | 1 | Н | Н | Brake           |

VSET[5..0]: Sets DAC output voltage. Refer to V

IN2: Along with IN1, sets state of outputs

IN1: Along with IN2, sets state of outputs

Table 1. Commanded Output Voltage (continued) OUTPUT VOLTAGE OUTPUT VOLTAGE VSET[5..0] VSET[5..0] 0x10h 1.29 0x30h 3.86 0x11h 1.37 0x31h 3.94 1.45 0x12h 0x32h

#### 7.6.1.2 REGISTER 1 - FAULT

The FAULT register is used to read the source of a fault condition, and to clear the status bits that indicated the fault. The register is defined as follows:

Table 8. Register 1 - Fault

| D7    | D6 - D5 | D4     | D3  | D2   | D1  | D0    |

|-------|---------|--------|-----|------|-----|-------|

| CLEAR | Unused  | ILIMIT | OTS | UVLO | OCP | FAULT |

CLEAR: When written to 1, clears the fault status bits

ILIMIT: If set, indicates the fault was caused by an extended current limit event

OTS: If set, indicates that the fault was caused by an overtemperature (OTS) condition

UVLO: If set, indicates the fault was caused by an undervoltage lockout OCP: If set, indicates the fault was caused by an overcurrent (OCP) event

FAULT: Set if any fault condition exists